## INTERNATIONAL STANDARD

# **ISO/IEC** 11518-1

First edition 1995-06-01

## Information technology — High-Performance Parallel Interface —

## Part 1:

Mechanical, electrical and signalling protocol specification (HIPPI-PH)

Technologies de l'information — Interface parallèle à haute performance —

Partie 1: Spécification du protocole mécanique, électrique et de signalisation (HIPPI-PH)

## ISO/IEC 11518-1:1995(E)

| Contents Page  |                                                          |                                                                                                                                                                                                                                                                                                                                                                  |                                  |  |  |  |  |  |  |

|----------------|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|--|--|--|--|--|--|

| Forewordv      |                                                          |                                                                                                                                                                                                                                                                                                                                                                  |                                  |  |  |  |  |  |  |

| Introductionvi |                                                          |                                                                                                                                                                                                                                                                                                                                                                  |                                  |  |  |  |  |  |  |

| 1              | Scope                                                    |                                                                                                                                                                                                                                                                                                                                                                  | 1                                |  |  |  |  |  |  |

| 2              | Definitio                                                | ons, editorial conventions, and abbreviations                                                                                                                                                                                                                                                                                                                    | 1                                |  |  |  |  |  |  |

| 3              | HIPPI structure                                          |                                                                                                                                                                                                                                                                                                                                                                  |                                  |  |  |  |  |  |  |

| ·              | 3.1<br>3.2                                               | Configuration characteristics<br>Logical framing hierarchy                                                                                                                                                                                                                                                                                                       | 2                                |  |  |  |  |  |  |

| 4              | Service 4.1 4.2 4.3 4.4 4.5 4.6 4.7 4.8 4.9 4.10 4.11    | Service primitives. Sequences of primitives Service primitives summary. Operational sequences Initiate connection service primitives Complete the connection service primitives. Flow control service primitives. Packet service primitives. Data transfer service primitives. Hangup service primitives. Control service primitives. Status service primitives. | 2<br>3<br>4<br>6<br>6<br>7       |  |  |  |  |  |  |

| 5              | 1nterface<br>5.1<br>5.2<br>5.3<br>5.4                    | e format and signals Physical framing hierarchy Data rate options Usage of signals Error detection                                                                                                                                                                                                                                                               | 10<br>11<br>11                   |  |  |  |  |  |  |

| 6              | State tra<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6      | ansitions State exit                                                                                                                                                                                                                                                                                                                                             | 14<br>14<br>14<br>15             |  |  |  |  |  |  |

| 7              | Timing 7.1 7.2 7.3 7.4 7.5 7.6 7.7 7.8 7.9               | Source CLOCK signal  Destination CLOCK signal  DATA BUS and PARITY BUS timing  Source control signals  I-Field information  LLRC  Destination control signals  Source wait gaps  Destination wait gaps                                                                                                                                                           | 21<br>22<br>22<br>22<br>22<br>22 |  |  |  |  |  |  |

| 8              | Physica<br>8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6<br>8.7 | Al characteristics  Differential circuit characteristics  INTERCONNECT signal characteristics  Ground signals  Reserved signals  Cable specifications  Cable grounding  Connector specifications  Connector pin assignments                                                                                                                                      | 23<br>24<br>24<br>24<br>25<br>25 |  |  |  |  |  |  |

### © ISO/IEC 1995

All rights reserved. Unless otherwise specified, no part of this publication may be reproduced or utilized in any form or by an means, electronic or mechanical, including photocopying and microfilm, without permission in writing from the publisher.

ISO/IEC Copyright Office • Case postale 56 • CH-1211 Genève 20 • Switzerland Printed in Switzerland

## © ISO/IEC

| Annex A              | Waveform examples                                |    |  |  |  |  |

|----------------------|--------------------------------------------------|----|--|--|--|--|

| A.1                  | Introduction                                     | 29 |  |  |  |  |

| A.2                  | Connection and start packet                      |    |  |  |  |  |

| A.3                  | End burst, start burst                           | 30 |  |  |  |  |

| A.4                  | End burst, end packet, start packet, start burst |    |  |  |  |  |

| A.5                  | End burst, end packet, disconnect                |    |  |  |  |  |

| A.6                  | Illegal end termination                          |    |  |  |  |  |

| <b>A</b> .7          | Rejected connection sequence                     |    |  |  |  |  |

| A.8                  | Aborted connection sequence                      | 33 |  |  |  |  |

| Annex B              | Implementation suggestions                       | 34 |  |  |  |  |

| B.1                  | Data rate option control                         | 34 |  |  |  |  |

| B.2                  | Source READY counter                             |    |  |  |  |  |

| B.3                  | I-Field sampling                                 |    |  |  |  |  |

| B.4                  | Short bursts                                     |    |  |  |  |  |

| B.5                  | Switching and the I-Field                        |    |  |  |  |  |

| B.6                  | Byte ordering                                    |    |  |  |  |  |

|                      | •                                                |    |  |  |  |  |

| Annex C              | Error checking                                   |    |  |  |  |  |

| C.1                  | Byte parity                                      |    |  |  |  |  |

| C.2                  | LLRC                                             |    |  |  |  |  |

| C.3                  | Burst length check                               |    |  |  |  |  |

| C.4                  | Sample LLRC circuit                              | 36 |  |  |  |  |

| Annex D              | Propagation delay calculation example            | 38 |  |  |  |  |

| D.1                  | CLOCK                                            | 38 |  |  |  |  |

| D.2                  | Loading data                                     |    |  |  |  |  |

| D.3                  | Cable skew                                       |    |  |  |  |  |

| D.4                  | Setup time                                       |    |  |  |  |  |

| D.5                  | Hold time                                        |    |  |  |  |  |

| D.6                  | Tuning delay                                     |    |  |  |  |  |

|                      | ·                                                |    |  |  |  |  |

|                      | Component options                                | 40 |  |  |  |  |

| E.1                  | Cable availability and colour coding             | 40 |  |  |  |  |

| E.2                  | Cable lengths                                    | 40 |  |  |  |  |

| E.3                  | Connector alignment guide                        |    |  |  |  |  |

| E.4                  | Maximum connector footprint                      |    |  |  |  |  |

| E.5                  | Connector availability                           |    |  |  |  |  |

| E.6                  | Connector jackscrew torque                       |    |  |  |  |  |

| E. 7                 | Line driver and receiver availability            | 40 |  |  |  |  |

|                      |                                                  |    |  |  |  |  |

| Alphahetic           | al index                                         | 43 |  |  |  |  |

| Alphabetical index40 |                                                  |    |  |  |  |  |

## ISO/IEC 11518-1:1995(E)

### Tables

| Table 1<br>Table 2<br>Table B<br>Table E | (<br>3. <b>1</b> i | Data rate options                                | . 26<br>. 35 |

|------------------------------------------|--------------------|--------------------------------------------------|--------------|

| Figures                                  |                    |                                                  |              |

| Figure 1                                 | ı                  | Control hierarchy                                | . vi         |

| Figure 2                                 | 2                  | Logical framing hierarchy                        | 2            |

| Figure 3                                 |                    | HIPPI-PH service interface                       |              |

| Figure 4                                 | 1                  | Initiate the connection service primitives       |              |

| Figure 5                                 |                    | Complete the connection service primitives       |              |

| Figure 6                                 | 6                  | Flow control service primitives                  |              |

| Figure 7                                 | 7                  | Packet service primitives                        | 6            |

| Figure 8                                 | _                  | Data transfer service primitives                 |              |

| Figure 9                                 | 9                  | Hangup service primitives                        |              |

|                                          | 10                 | Control service primitives                       |              |

|                                          | 11                 | Status service primitives                        | 9            |

| -                                        | 12                 | Physical framing hierarchy                       | . 10         |

|                                          | 13                 | Interface signal summary                         | . 10         |

|                                          | 14                 | Data packing                                     | . 12         |

| 9                                        | 15                 | Source READY flow diagram                        |              |

|                                          | 16                 | Destination READY flow diagram                   |              |

|                                          | 17                 | Source flow diagram                              |              |

|                                          | 18                 | Destination flow diagram                         | . IS         |

|                                          | 19                 | Source driven signals at the Source              | 21           |

|                                          | 20<br>21           | Differential circuit                             | 22           |

|                                          | 21<br>22           | INTERCONNECT circuit                             |              |

| _                                        | 22<br>23           | Cable connector – tabs                           |              |

|                                          | 23<br>24           | Bulkhead connector – receptacle                  |              |

| _                                        | 24<br>A.1          | Typical HIPPI-PH waveforms                       |              |

| •                                        | A.2                | Connect, start packet, start burst               | 30           |

| <b>J</b>                                 | A.3                | End burst, start burst                           | 30           |

| -                                        | A.4                | End burst, end packet, start packet, start burst | 31           |

| 3                                        | A.5                | End burst, end packet, disconnect                | . 31         |

|                                          | A.6                | Illegal end termination                          | . 32         |

|                                          | A.7                | Rejected connection sequence                     | . 32         |

| •                                        | A.8                | Aborted connection sequence                      | . 33         |

| 9                                        | B.1                | Physical layer switching                         |              |

| •                                        | B.2                | Switching with intermediate nodes                | . 35         |

|                                          | B.3                | Ordered byte stream mapping                      |              |

| •                                        | B.4                | Bit significance within byte 0                   | . 35         |

| Figure                                   | C.1                | Parity and LLRC example                          | . 37         |

| Figure                                   | C.2                | Representative LLRC circuit                      | . 37         |

| Figure                                   | D.1                | Propagation delay example block diagram          | . 39         |

|                                          | E.1                | Connector alignment guide                        | . 42         |

| Figure                                   | E.2                | Maximum connector footprint                      | . 42         |

### **Foreword**

ISO (the International Organization for Standardization) and IEC (the International Electrotechnical Commission) form the specialized system for worldwide standardization. National bodies that are members of ISO or IEC participate in the development of International Standards through technical committees established by the respective organization to deal with particular fields of technical activity. ISO and IEC technical committees collaborate in fields of mutual interest. Other international organizations, governmental and non-governmental, in liaison with ISO and IEC, also take part in the work.

In the field of information technology, ISO and IEC have established a joint technical committee, ISO/IEC JTC 1. Draft International Standards adopted by the joint technical committee are circulated to national bodies for voting. Publication as an International Standard requires approval by at least 75 % of the national bodies casting a vote.

International Standard ISO/IEC 11518-1 was prepared by Joint Technical Committee ISO/IEC JTC 1, *Information technology*, Subcommittee SC 25, *Interconnection of information technology equipment*.

ISO/IEC 11518 consists of the following parts, under the general title *Information technology — High-Performance Parallel Interface*:

- Part 1: Mechanical, electrical and signalling protocol specification (HIPPI-PH)

- Part 2: Framing Protocol (HIPPI-FP)

- Part 3: Encapsulation of ISO 8802-3 Logical link control protocol data units (HIPPI-LE)

- Part 4: Mapping of HIPPI to IPI device generic command sets (HIPPI-IPI)

- Part 5: Memory Interface (HIPPI-MI)

- Part 6: Physical Switch Control (HIPPI-SC)

Annexes A to E of this part of ISO/IEC 11518 are for information only.

### Introduction

This part of ISO/IEC 11518 defines the physical layer of an efficient simplex high-performance point-to-point interface operating at speeds of 800 or 1 600 Mbit/s. The -PH abbreviation stands for "physical layer".

Characteristics of this HIPPI physical layer interface include

- point-to-point connections use one or two copper twisted-pair cables for distances of up to 25 m.

- the HIPPI-PH is a simplex interface, capable of transferring data in one direction only. Two HIPPI-PHs may be used to implement a full-duplex interface.

- data transfers are performed and flow controlled in increments of bursts, each burst normally containing 256 words.

- signalling and control sequences are kept simple, and a look-ahead flow control is used, to allow average transfer rates for large file transfers to approach the peak transfer rate, even over distances longer than specified for the HIPPI-PH cables.

- $-\,$  the HIPPI-PH provides support for low-latency, real-time, and variable size packet transfers.

- the HIPPI-PH is designed to facilitate use in a circuit-switched environment. In support of this feature, a limited information field is available for subdevice addressing or other nonspecified control functions during the connection phase of operation. One round-trip cable delay is required to establish or terminate a connection.

- the HIPPI-PH is also designed to transmit multiple packets after a connection has been established. No round-trip cable delays are required between packets.

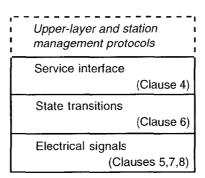

Figure 1 shows the interrelationship of the different clauses of this part of ISO/IEC 11518. The upper-layer protocols and station management protocols are not covered in this part of ISO/IEC 11518.

Figure 1 - Control hierarchy

## Information technology – High-Performance Parallel Interface –

## Part 1:

Mechanical, electrical, and signalling protocol specification (HIPPI-PH)

## 1 Scope

This part of ISO/IEC 11518 provides the mechanical, electrical and signalling protocol specifications for an efficient simplex high-performance point-to-point interface between pieces of data-processing equipment.

The interface described in this part of ISO/IEC 11518 can be operated at peak data rates of 800 or 1 600 Mbit/s, over distances of up to 25 m by means of copper cabling. A distance-independent signalling protocol allows the average data rates to approach the peak data rates, even over distances longer than specified for the HIPPI-PH.

The purpose of this part of ISO/IEC 11518 is to facilitate the development and use of computer systems by providing a common interface at the physical and data framing layers. It provides an efficient interconnection between computers, high-performance display systems, and high-performance, intelligent block-transfer peripherals. The interface is optimized for large block transfers.